# FPGA-based Reconfigurable On-board Computing Systems for Space Applications

A thesis accepted by the Faculty of Aerospace Engineering and Geodesy of the Universität Stuttgart in partial fulfilment of the requirements for the degree of Doctor of Engineering Sciences (Dr.-Ing.)

#### by

## M. Eng. Toshinori Kuwahara

born in Kumamoto, Japan

| main   | referee: |

|--------|----------|

| co-ref | eree:    |

Prof. Dr. rer. nat. Hans-Peter Röser Prof. Dr. Eng. Tetsuo Yasaka

Date of defence:

October 29, 2009

Institute of Space Systems Universität Stuttgart 2010

## Abstract

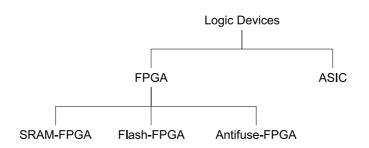

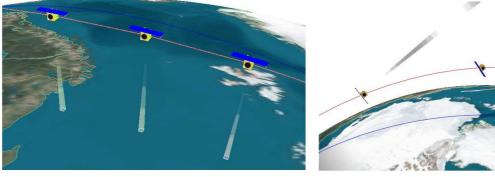

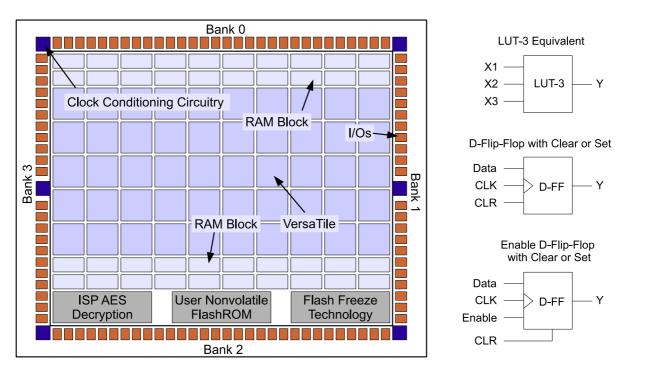

The purpose of the thesis is to conceptualize an application method of ground-based reconfigurable FPGA (Field Programmable Gate Array) technologies for space systems and to apply the method to the on-board computer of the small satellite *Flying Laptop* for the on-orbit demonstration. The *Flying Laptop* satellite is the first small satellite within the "Stuttgart small satellite program" in which several small satellites are developed by the Institute of Space Systems at the Universität Stuttgart. The main mission of the *Flying Laptop* is to demonstrate the space use of reconfigurable FPGAs for the "reconfigurable computing" on an central on-board computer aboard a spacecraft. Due to their radiation vulnerabilities reconfigurable FPGAs have not yet been employed in practical space applications with high reliability requirements. The *Flying Laptop* project aims to achieve the world's first orbit demonstration of a purely FPGA-based central on-board computer.

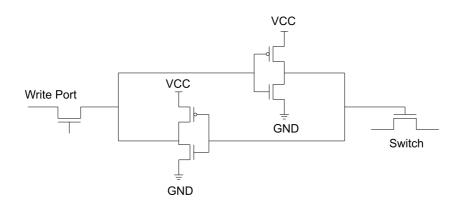

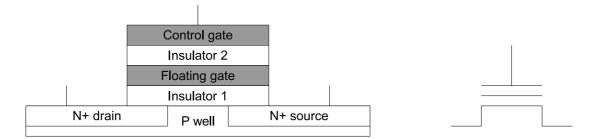

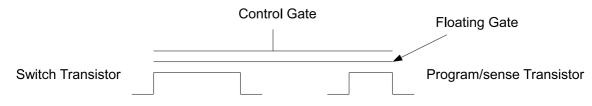

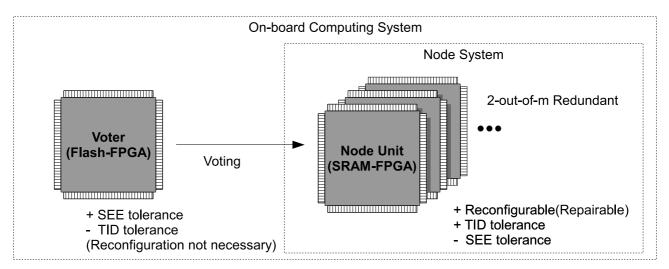

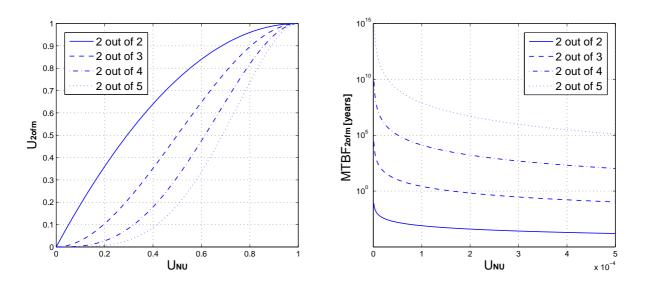

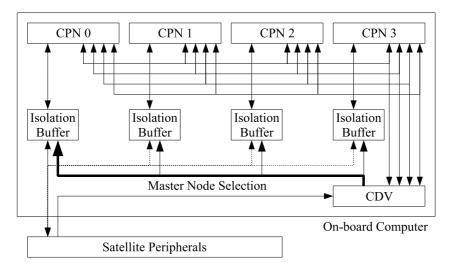

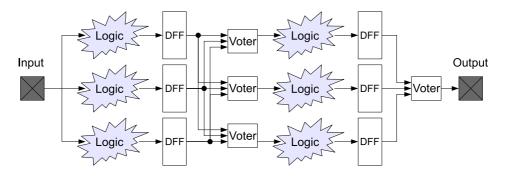

Within this research firstly, application methods of reconfigurable FPGAs for space systems were investigated, which are not limited to small satellites but for general space systems. The investigation is based on thorough experimental data survey and analysis of radiation effects on existing FPGA devices. Main radiation effects of single event effects and total ionizing dose effects were extensively investigated. Based on the data obtained, a combinational use of SRAM-FPGAs (multi-chip redundant) and Flash-FPGAs (voting element) for mitigating radiation effects was conceptualized. A mathematical system reliability analysis of repairable multi-redundant systems has been conducted and reliability models of "2-out-of-m" systems were established. The analysis illustrates that a multi-redundant system based on SRAM-FPGAs together with a Flash-FPGA based voter provides a sufficiently high reliability for Low Earth Orbit (LEO) missions against radiation effects.

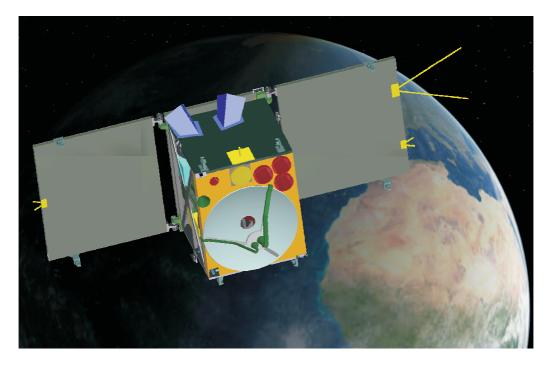

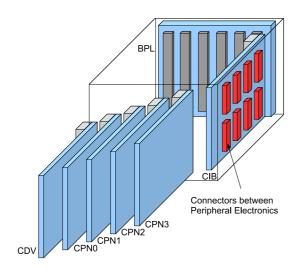

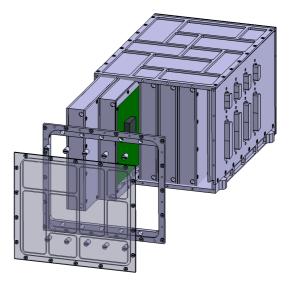

After the conceptualization of application methods of reconfigurable FPGAs for the space environment, it is applied to the on-board computer of the small satellite *Flying Laptop. Flying Laptop* is a cubic, 3-axis stabilized satellite with the edge lengths of about  $600 \text{ mm} \times 700 \text{ mm} \times 800 \text{ mm}$  and a mass of about 120 kg, which shall be launched into sunsynchronous LEO in an altitude of around 600 km. A system architecture with four SRAM-FPGA based central processing nodes and one Flash-FPGA based voter was applied for the on-board computer of the *Flying Laptop*. This on-board computer is the central computing system aboard the satellite and shall be capable of controlling all satellite peripheral electronics. First of all, the system design of the whole satellite has been conducted within the scope of the thesis in order to allow the design of the on-board computer. Based on the established system requirements, the on-board computer of the *Flying Laptop* was designed and the breadboard model and partly the engineering model of its components are developed.

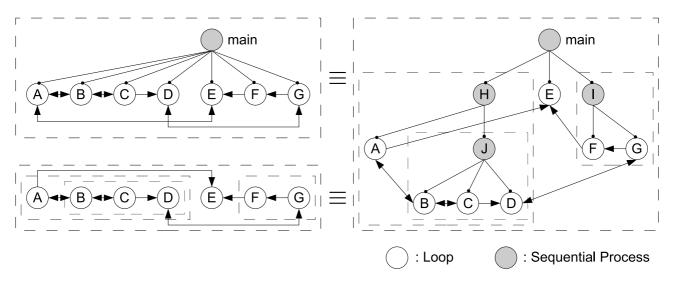

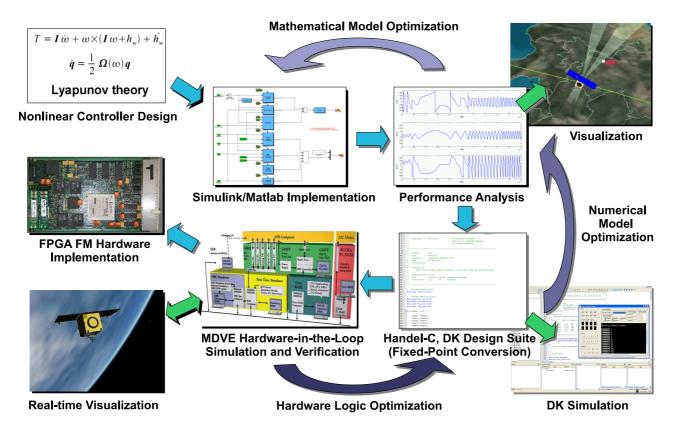

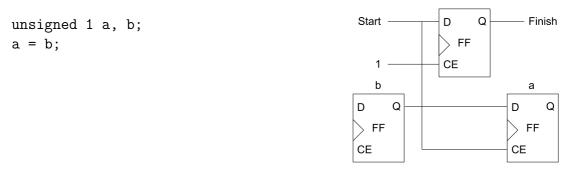

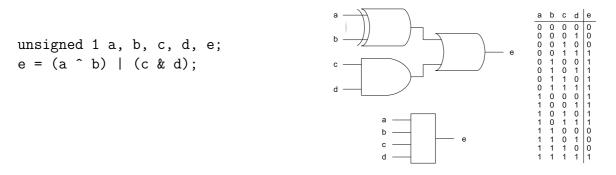

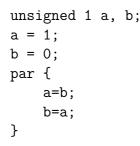

The hardware logic (control algorithm) which shall be implemented into FPGAs can be designed by means of hardware description languages. However, it is no longer software engineering but hardware engineering for generating real hardware logics inside FPGAs which are executed in parallel in real-time. The implementation of the complete satellite control algorithms into FPGAs is the world's first achievement. By means of the breadboard model assembly, the control algorithm of the *Flying Laptop* is developed in such a way that the computational capability of FPGAs can be maximized by utilizing their internal massive parallelism. The satellite main functions are designed, developed, and implemented in FPGAs by means of the hardware description languages Handel-C and VHDL. The thesis provides development methods of the control algorithms. In addition to this, a control algorithm development facility has been established for the further design activities.

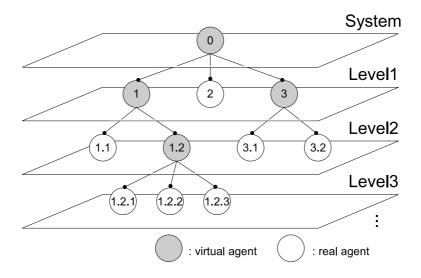

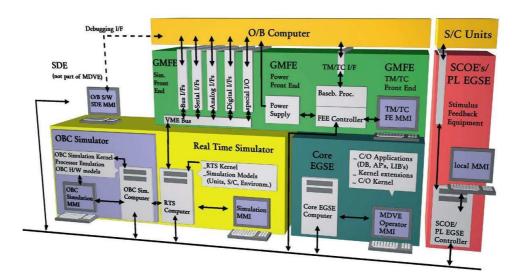

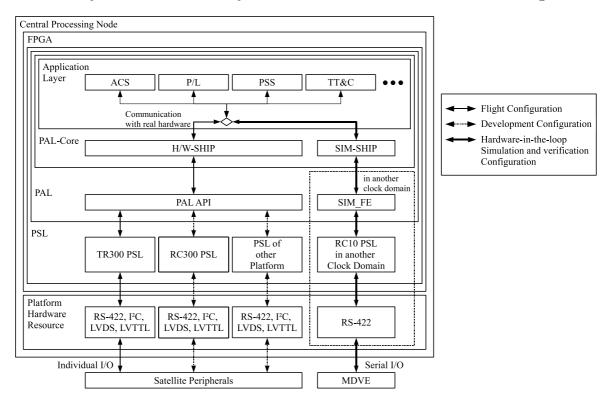

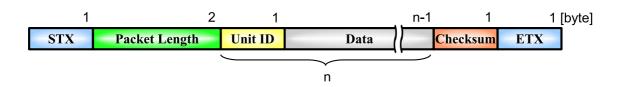

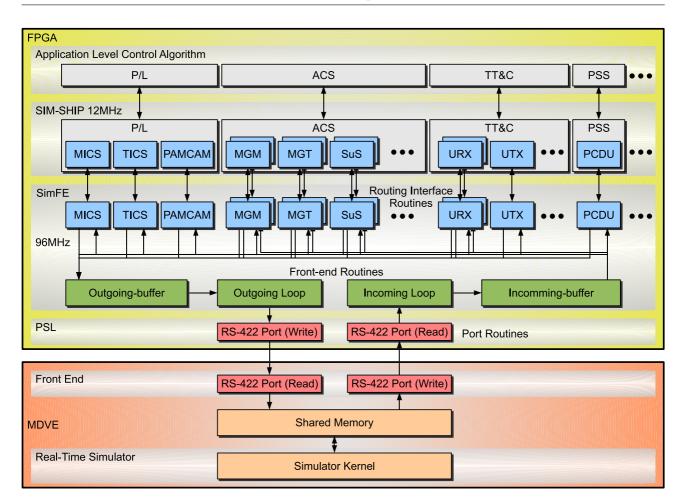

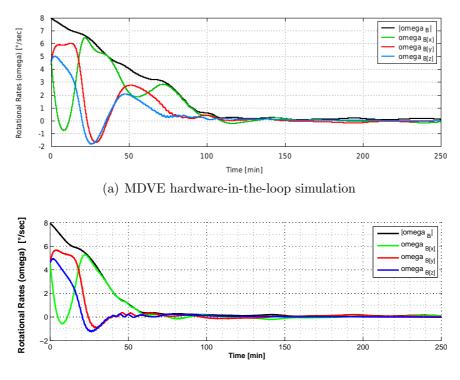

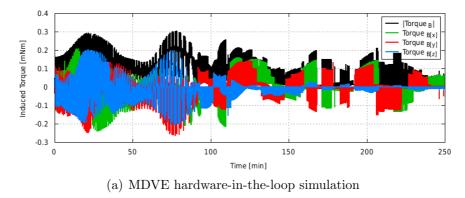

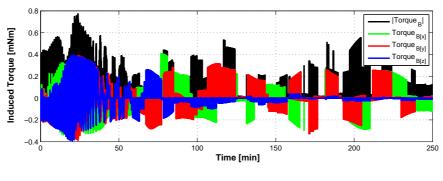

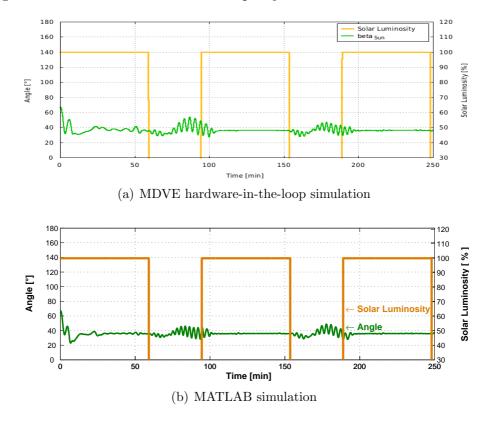

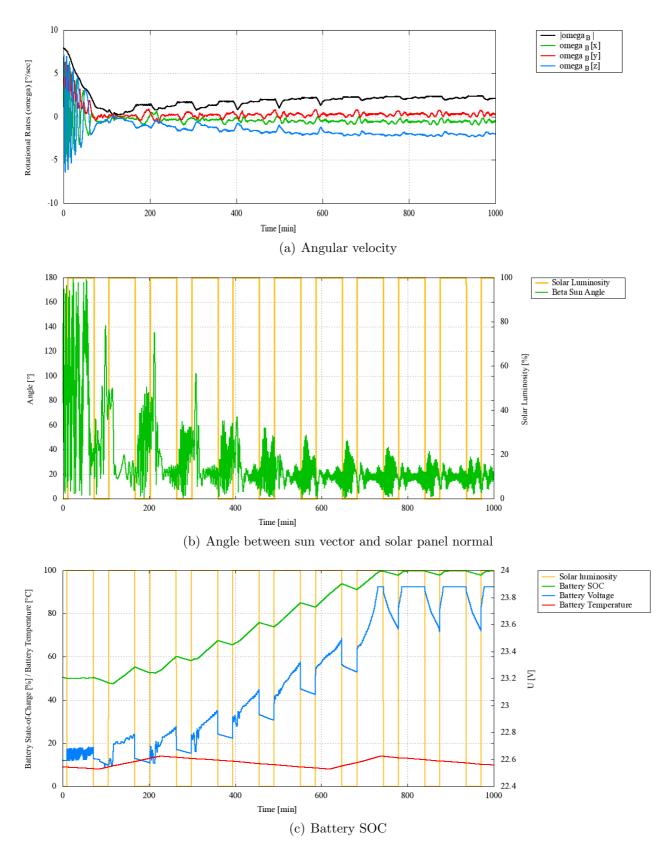

Finally, the developed control algorithms are verified in a simulation and verification environment in order to prove the validities of the above described developments. First of all, an FPGA hardware-in-the-loop real-time simulation environment has been established based on the Model-based Development and Verification Environment (MDVE). MDVE was established at the Institute of Space Systems supported by EADS Astrium. The communication interface between the MDVE and FPGAs are developed, including the required hardware components and the serialization algorithms of communication lines inside an FPGA. Using this simulation and verification environment, extensive simulations have been conducted and the design of the on-board computer, as well as the system design of the whole satellite are validated. At the end, an extended investigation has been conducted on formal verification methods of the hardware-logic in order to provide the way of strict design verifications. The formal semantics of Handel-C are extended to enable simultaneous communications between multiple hardware logic elements, which will be able to realize secure implementation of parallel hardware logic into FPGAs for future space applications.

This thesis establishes the basis of principle application methods of reconfigurable FPGA technologies for "reconfigurable computing" on space systems which provides innovative solutions for high computational demands of future space applications.

# Zusammenfassung

Das Ziel dieser Dissertation ist der Entwurf eines Verfahrens zum Einsatz von herkömmlichen FPGA (Field Programmable Gate Array) Technologien für die Raumfahrt und die Demonstration dieses Verfahrens als Bordrechner des Kleinsatelliten *Flying Laptop*. Der *Flying Laptop* ist der erste von mehreren Kleinsatelliten, der im Rahmen des "Stuttgarter Kleinsatellitenprogrammes," am Institut für Raumfahrtsysteme der Universität Stuttgart entwickelt wird. Der Haupteinsatz des *Flying Laptop* ist die Demonstration von rekonfigurierbaren FPGAs im Weltraum zum "Reconfigurable Computing" auf einem zentralen Bordrechner eines Raumfahrzeugs. Dies wurde wegen der Strahlungsanfälligkeit dieser Bauteile bisher nicht in Raumfahrtsystemen mit hoher Zuverlässigkeitsanforderung verwendet. Der *Flying Laptop* wird als weltweit erstes Raumfahrzeug einen reinen FPGA-basierten Bordrechner verwenden.

Im Rahmen dieser Arbeit wurden zuerst die Anwendungsverfahren der rekonfigurierbaren FPGAs für Raumfahrtsysteme erforscht, die nicht nur für Kleinsatelliten, sondern auch für allgemeine Raumfahrtsysteme gelten. Die Forschung basiert auf einer vollständigen Recherche über experimentelle Daten und Analysen der Strahlungsanfälligkeit vorhandener FPGA-Bauteile. Die Hauptauswirkungen von "Single Event Effects" und "Total Ionizing Dose" wurden ausführlich untersucht. Ausgehend von den erhaltenen Daten wurde ein kombinierter Einsatz der SRAM-FPGAs (multi-chip redundant) und Flash-FPGAs (voting element) entworfen, um die Strahlungsanfälligkeit zu reduzieren. Eine mathematische Systemzuverlässigkeitsanalyse der wiederherstellbaren Multi-Redundantsystemen wurde durchgeführt und das Zuverlässigkeitsmodell von "2-out-of-m" Systemen wurde aufgestellt. Diese Analysen stellen dar, dass ein Multi-Redundantsystem mit SRAM-FPGAs zusammen mit einem Flash-FPGA basierten Voter trotz Strahlungsanfälligkeit in einer niedrigen Erdumlaufbahn eine hinreichende Zuverlässigkeit gewährleistet.

Dieses Implementierungsverfahren der rekonfigurierbaren FPGAs für die Weltraumumgebung wurde nach dem Entwurf für den Bordrechner des Kleinsatelliten *Flying Laptop* angewendet. Der *Flying Laptop* ist ein würfelförmiger dreiachsenstabilisierter Satellit mit den Kantenlängen von etwa 600 mm  $\times$  700 mm  $\times$  800 mm und einer Masse von etwa 120 kg, der in einer sonnensynchronen niedrigen Erdumlaufbahn mit einer Höhe von etwa 600 km eingesetzt werden soll. Eine Systemarchitektur mit vier SRAM-FPGA basierten "Central Processing Nodes" und einem Flash-FPGA basierten Voter wurde für den Bordrechner des *Flying Laptop* festgelegt. Dieser Bordrechner ist das zentrale Rechensystem auf dem Satelliten, das alle Satellitenkomponenten steuern soll. Als Erstes wurde im Rahmen der Dissertation das Systemdesign des ganzen Satellitensystems durchgeführt, um das Design des Bordrechners zu ermöglichen. Basierend auf den festgestellten Systemanforderungen wurde der Bordrechner des *Flying Laptop* ausgelegt. Außerdem wurden ein Breadboard-Modell des Bordrechners und teilweise die Engineering-Modelle seiner Komponenten entwickelt.

Die Hardwarelogik (Steuerungsalgorithmen), die in den FPGAs implementiert werden sollen, können mit Hardwarebeschreibungssprachen entwickelt werden. Es handelt sich hierbei also nicht mehr um Softwareentwicklung, sondern um Hardwareentwicklung. Dabei wird die echte Hardwarelogik in den FPGAs produziert, die parallel in Echtzeit abgearbeitet wird. Die Implementierung der kompletten Steuerungsalgorithmen eines Satelliten in FPGAs ist weltweit einzigartig. Mittels des Breadboard-Modells wurden die Steuerungsalgorithmen des *Flying Laptop* so entwickelt, dass die Rechenleistungen der FPGAs unter Ausnutzung massiver Parallelität maximiert werden. Die Hauptfunktionen des Satelliten wurden mit den Hardwarebeschreibungssprachen Handel-C und VHDL ausgelegt, entwickelt, und in die FPGAs implementiert. Die Dissertation stellt die Entwicklungsstrategie für die Steuerungsalgorithmen bereit. Zusätzlich wurde die Infrastruktur für weitere Designaktivitäten aufgebaut.

Schließlich wurden die Steuerungsalgorithmen in einer Simulations- und Verifikationsumgebung geprüft. Dafür wurde zunächst eine "Hardware-in-the-Loop"-Simulationsumgebung aufgebaut, die auf einer Modell-basierten Entwicklungs- und Verifikationsumgebung (Model-based Development and Verifikation Environment (MDVE)) basiert. Die MDVE wurde mit Unterstützung von EADS Astrium am Institut für Raumfahrtsysteme zur Verfügung gestellt. Die Kommunikationsschnittstelle zwischen MDVE und FPGAs wurde entwickelt, einschließlich der benötigten Hardwarekomponenten und des Algorithmus, welcher die Kommunikationskanäle innerhalb einem FPGA in serielle Reihenfolge bringt. Mittels dieser Simulations- und Verifikationsumgebung wurden ausführliche Simulationen durchgeführt. Daraus resultierend wurde die Gültigkeit des Bordrechnerdesigns sowie das Systemdesigns für den gesamten Satelliten validiert. Schlussendlich wurde eine erweiterte Untersuchung über formale Verifikationsverfahren der Steuerungsalgorithmen durchgeführt, um eine strikte Designverifikation zu ermöglichen. Die formale Semantik von Handel-C wurde erweitert, um die gleichzeitige Kommunikation zwischen mehreren Hardwarelogikelementen zu ermöglichen. Diese Untersuchung stellt eine formale Verifikation der parallel laufenden Hardwarelogikelemente in Aussicht. Dadurch würde die verlässliche Implementierung von betriebssicherer Hardwarelogik in die FPGAs für zukünftige Raumfahrtanwendungen ermöglicht.

Diese Dissertation legt die Basis für ein Anwendungsverfahren von rekonfigurierbaren FPGA-Technologien auf Raumfahrzeugen. Dieses Verfahren stellt eine innovative Lösung für erhöhte Rechenanforderungen von zukünftigen Raumfahrtanwendungen dar.

# Contents

| Abstra                     | act                                                                      | i                                                                                     |

|----------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Zusan                      | nmenfassung                                                              | iii                                                                                   |

| List o                     | f Figures                                                                | x                                                                                     |

| List o                     | f Tables                                                                 | xiii                                                                                  |

| Acron                      | yms                                                                      | xiv                                                                                   |

| Nome                       | nclature                                                                 | xvii                                                                                  |

| $0.1 \\ 0.2 \\ 0.3 \\ 0.4$ | 0.2.1. FPGA and reconfigurable computing                                 | 1<br>1<br>2<br>2<br>3<br>3<br>4<br>5                                                  |

|                            |                                                                          | 5                                                                                     |

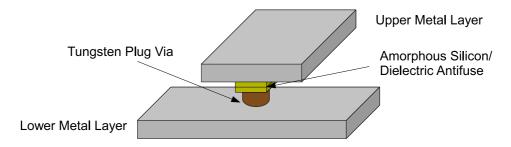

| 1.1<br>1.2                 | 1.2.1. Mechanism of programmable elements                                | $\begin{array}{c} 6\\ 7\\ 7\\ 10\\ 10\\ 11\\ 11\\ 11\\ 13\\ 13\\ 13\\ 13 \end{array}$ |

|                            | 1.4.3.       SEEs on SRAM-FPGAs         1.4.4.       SEEs on Flash-FPGAs | 14<br>18<br>v                                                                         |

|     | 1.5. | Summary                                                   | 18              |

|-----|------|-----------------------------------------------------------|-----------------|

| 2.  | Арр  | lication method of reconfigurable FPGAs for space systems | 19              |

|     | 2.1. | Combinational use of different types of FPGAs             | 19              |

|     | 2.2. | System reliability analysis                               | 20              |

|     |      | 2.2.1. Basic probability theory                           | 21              |

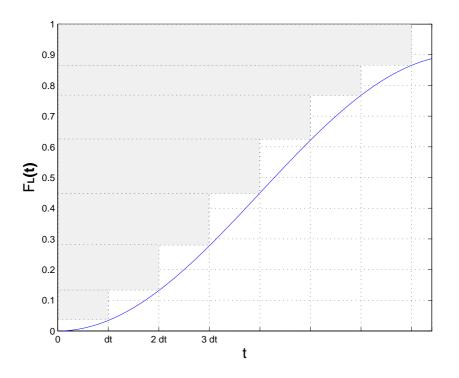

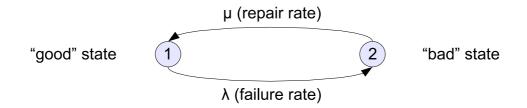

|     |      | 2.2.2. Reliability modeling of repairable single node     | 21              |

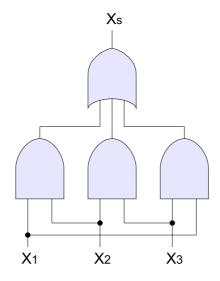

|     |      | 2.2.3. 2-out-of-3 systems modeling                        | 23              |

|     |      | 2.2.4. 2-out-of-m systems with identical components       | 25              |

|     | 2.3. | Reliability against TID effects                           | 26              |

|     |      | 2.3.1. Reliability of voter against TID effects           | 27              |

|     |      | 2.3.2. Reliability of node system against TID effects     | 28              |

|     | 2.4. | Node system design                                        | 29              |

|     |      | 2.4.1. Trade-off on degree of redundancy                  | 29              |

|     |      | 2.4.2. Node system reliability after latest repair        | $\frac{-0}{30}$ |

|     |      | 2.4.3. Effect of periodic preventive renewals             | 31              |

|     | 2.5. | Summary                                                   | 31              |

|     | 2.0. | Summary                                                   | 91              |

| 11. | De   | emonstration with the small satellite Flying Laptop       | 33              |

|     |      |                                                           |                 |

| 3.  | -    | ng Laptop satellite                                       | 34              |

|     | 3.1. | Flying Laptop project                                     | 35              |

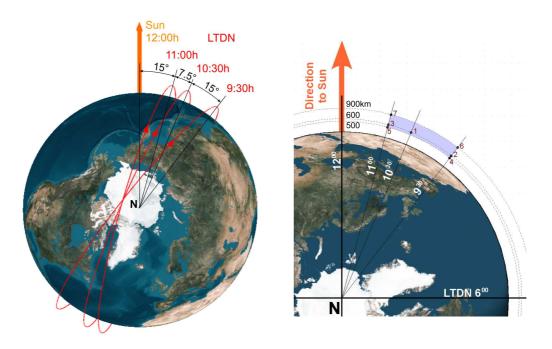

|     | 3.2. | Mission description                                       | 36              |

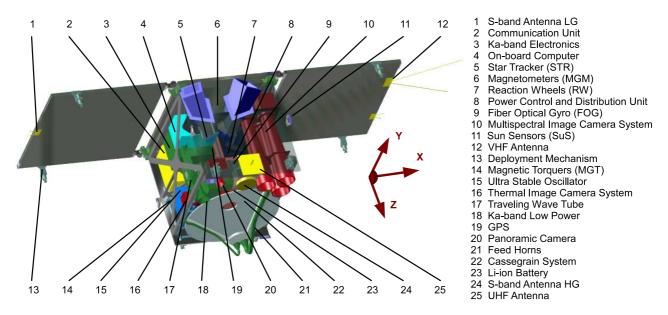

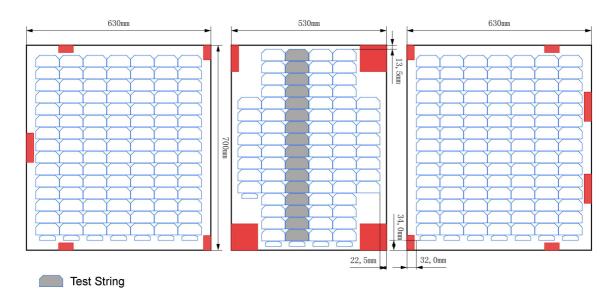

|     | 3.3. | Scientific payload instruments                            | 37              |

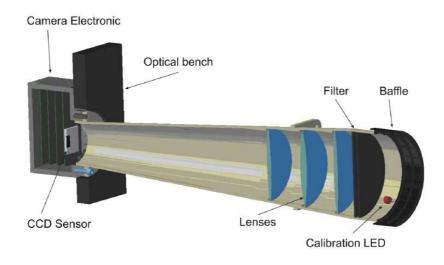

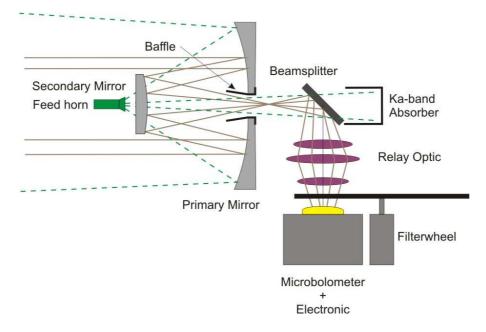

|     |      | 3.3.1. Camera systems                                     | 37              |

|     |      | 3.3.2. Scientific communication systems                   | 39              |

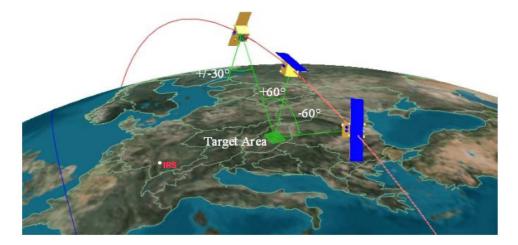

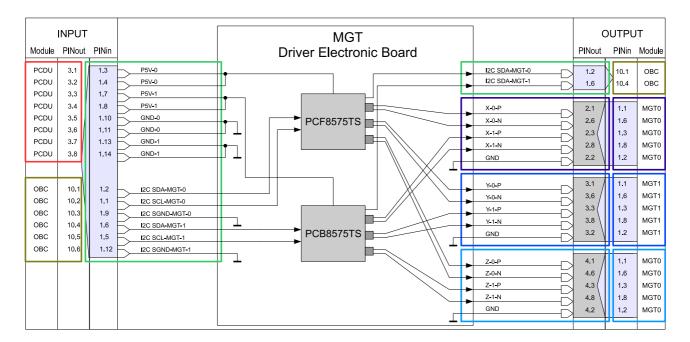

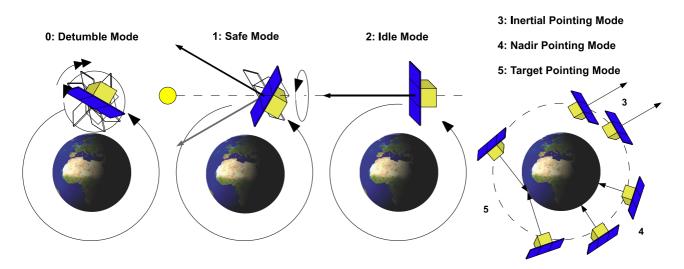

|     | 3.4. | Attitude control system                                   | 39              |

|     |      | 3.4.1. Attitude pointing modes                            | 40              |

| 4.  | Syst | em design of the Flying Laptop                            | 42              |

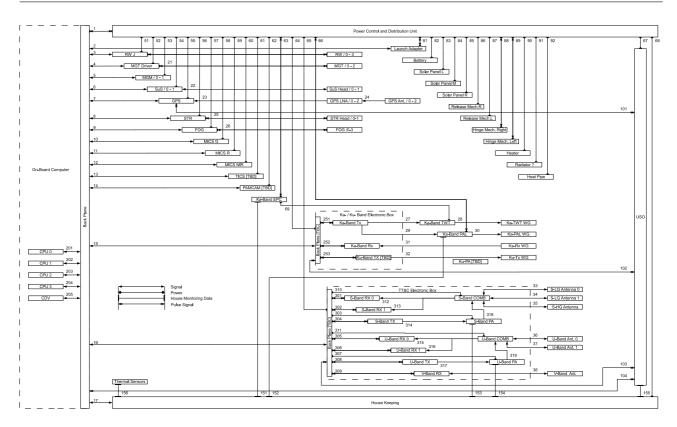

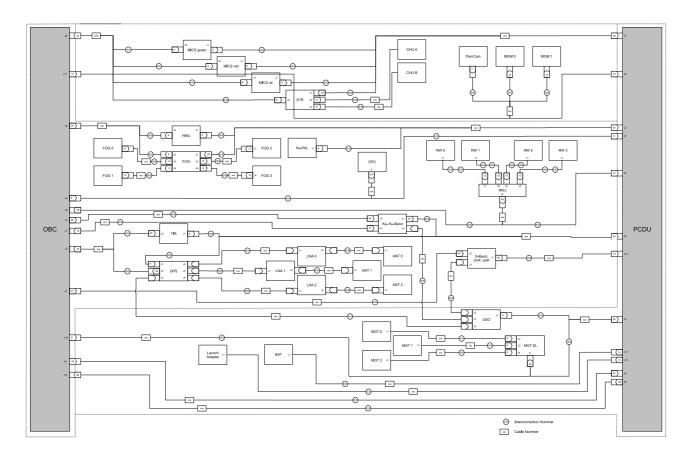

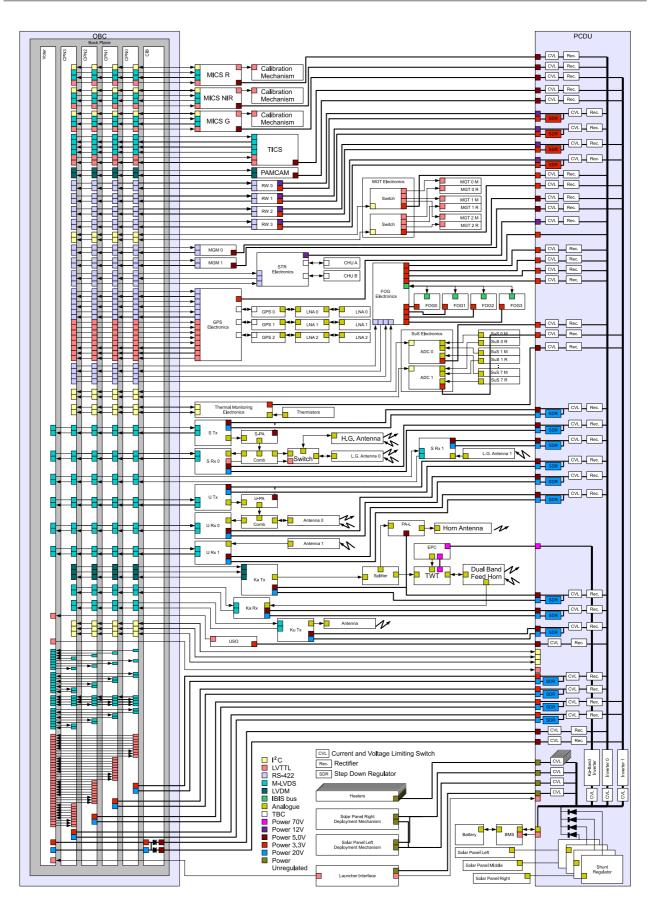

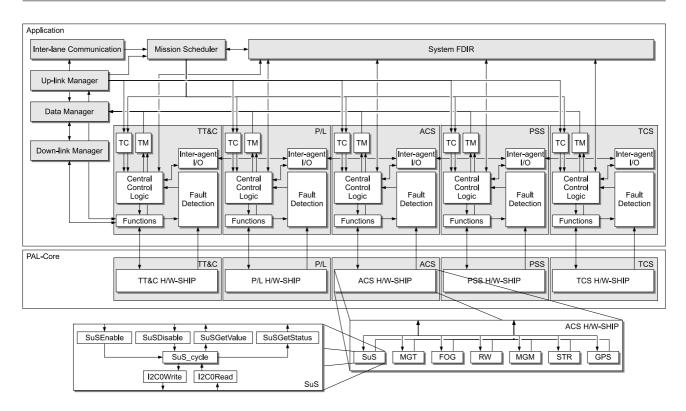

|     | 4.1. | Electrical architecture design                            | 44              |

|     |      | 4.1.1. Electrical interconnections block diagram          | 44              |

|     |      | 4.1.2. Input/Output diagram                               | 44              |

|     |      | 4.1.3. Mock-up model development                          | 45              |

|     |      | 4.1.4. Harness cabling plan                               | 46              |

|     | 4.2. | System electrical architecture                            | 47              |

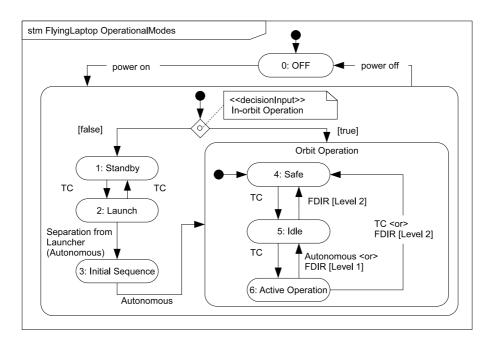

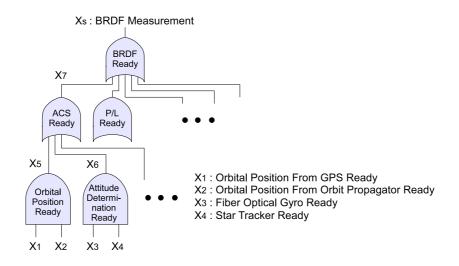

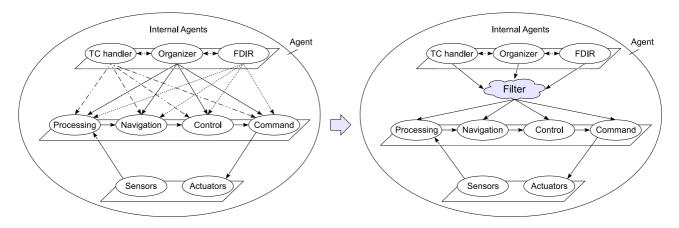

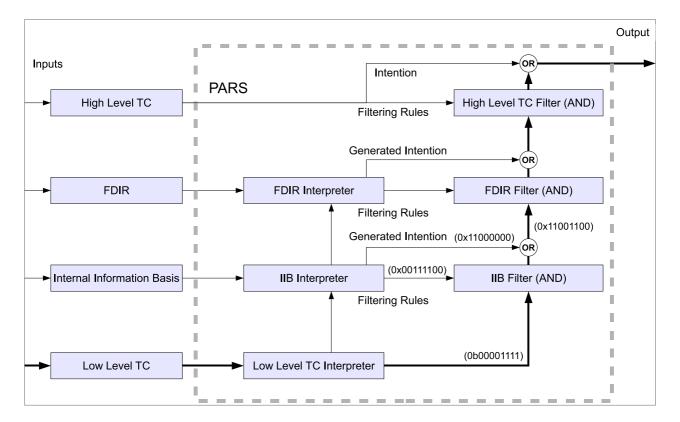

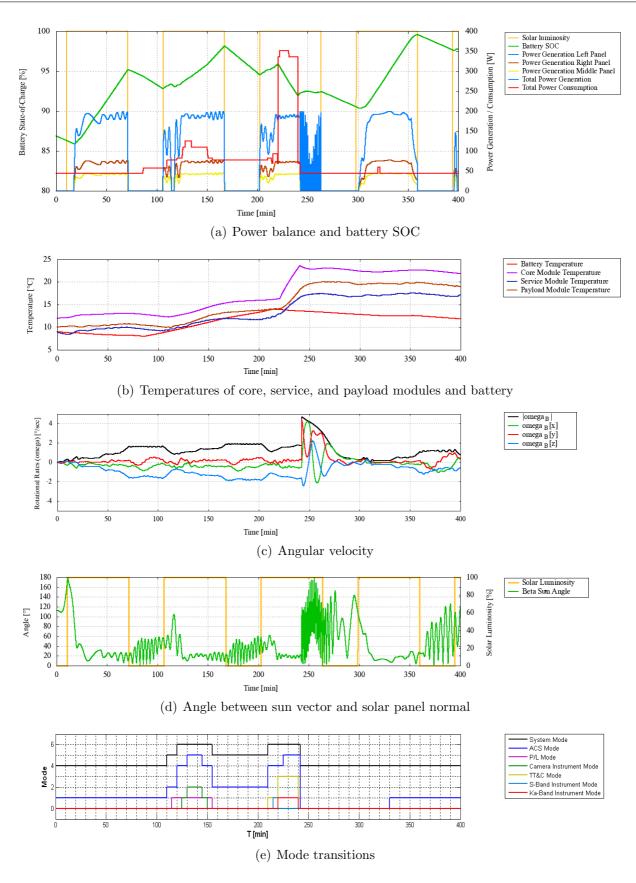

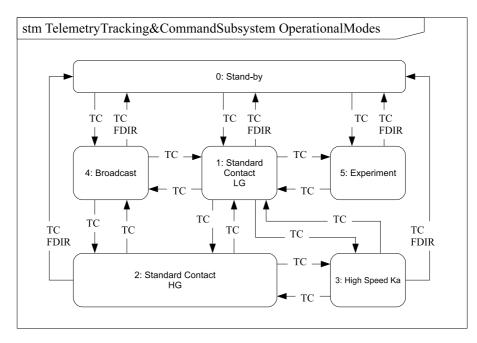

|     | 4.3. | Operational design                                        | 49              |

|     | 1.0. | 4.3.1. Operational design concept                         | 49              |

|     |      | 4.3.2. Operational mode design                            | -19<br>50       |

|     |      | 1                                                         | 50              |

|     |      | 5 I                                                       | $50 \\ 51$      |

|     |      | 4.3.4. Data handling                                      |                 |

|     |      | 4.3.5. Communication structure                            | 52              |

|     | 4 4  | 4.3.6. Contingency operation                              | 52              |

|     | 4.4. | Attitude control                                          | 53              |

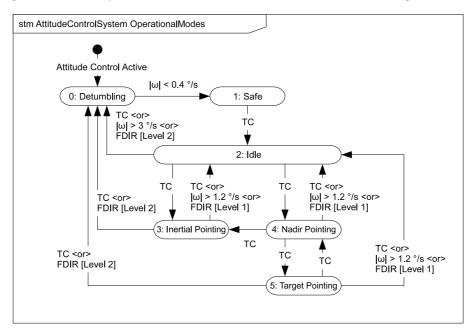

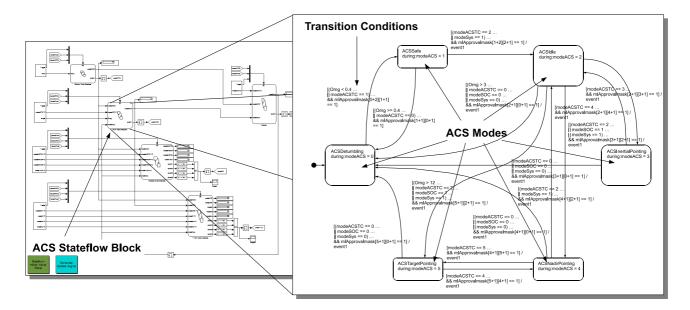

|     |      | 4.4.1. Attitude control modes                             | 53              |

|     |      | 4.4.2. Attitude control system state-machine              | 53              |

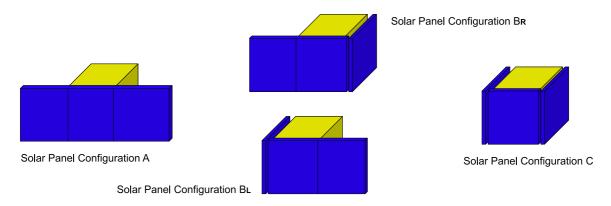

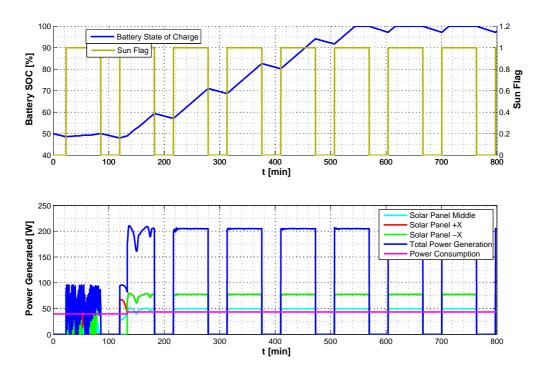

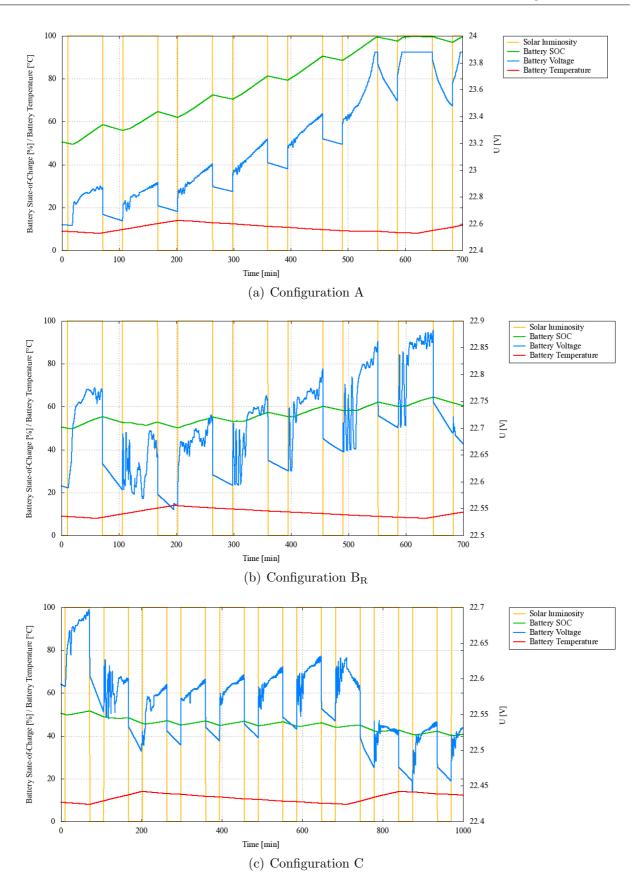

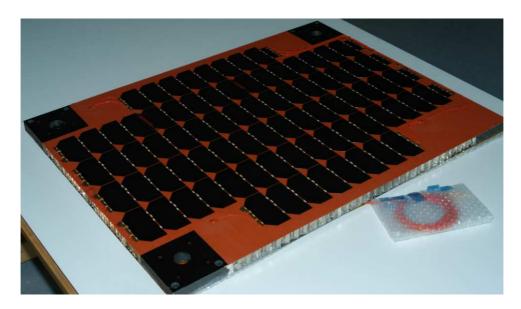

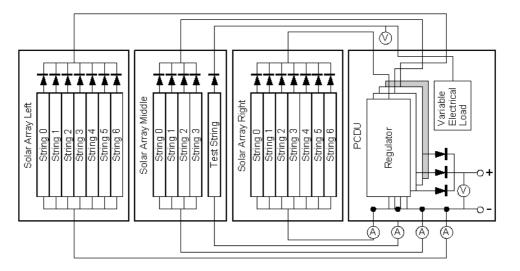

|    | 4.5.                                                          | Power balancing design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 54                                                                                                                                                                                             |

|----|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                               | 4.5.1. Launch and early orbit phase scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    |                                                               | 4.5.2. Analysis of failure scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    |                                                               | 4.5.3. Analysis of a maximum power consumption scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    | 4.6.                                                          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

| 5. |                                                               | sign of OBC hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                                                                                               |

|    |                                                               | Requirements of OBC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

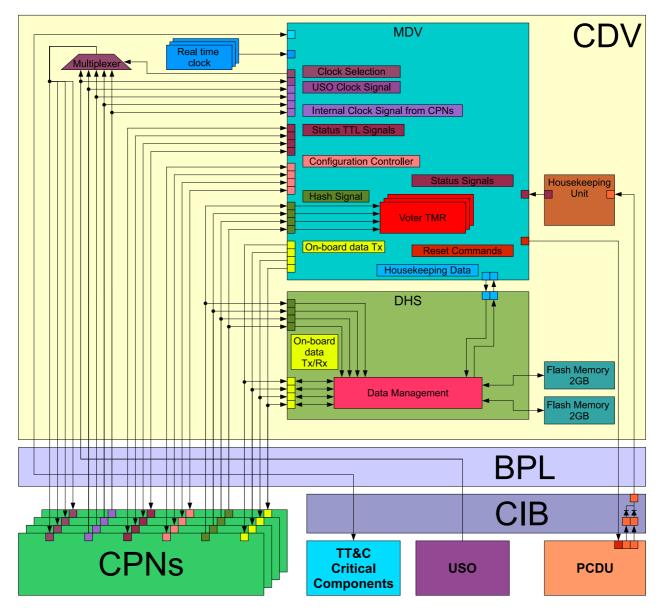

|    | 5.2.                                                          | Applied OBC design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    | 5.3.                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    | 5.4.                                                          | Functional requirements allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                     |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

|    |                                                               | 5.4.1. FDIR strategy $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                     |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 65                                                                                                                                                                                             |

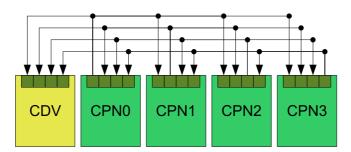

|    |                                                               | 5.4.2. Node system configuration and interface replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 65                                                                                                                                                                                             |

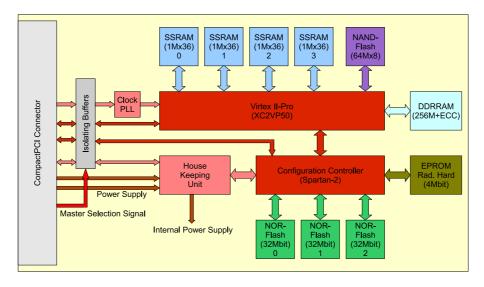

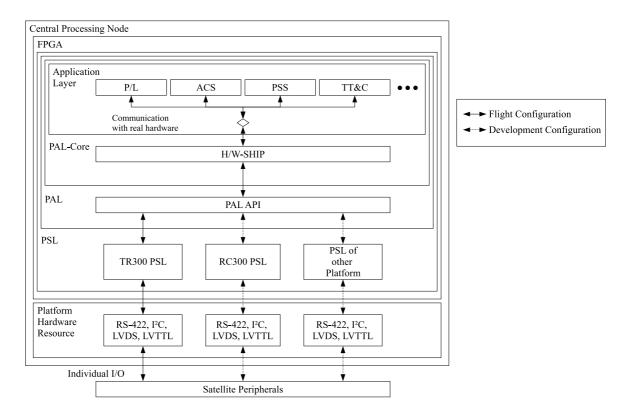

|    | 5.5.                                                          | Design implementation of CPN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 66                                                                                                                                                                                             |

|    |                                                               | 5.5.1. Node structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 66                                                                                                                                                                                             |

|    |                                                               | 5.5.2. Interface isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |

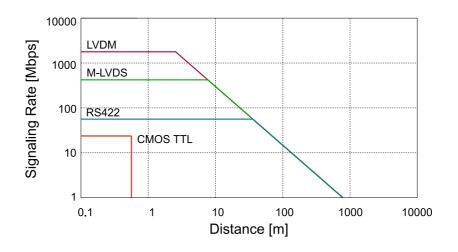

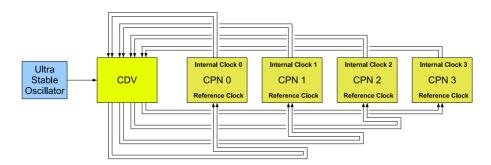

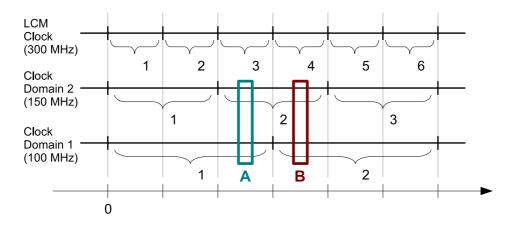

|    |                                                               | 5.5.3. System clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 67                                                                                                                                                                                             |

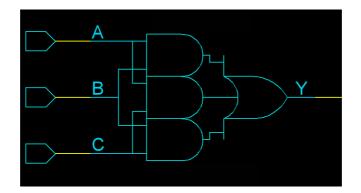

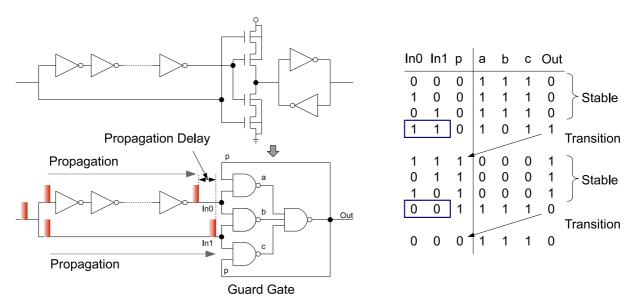

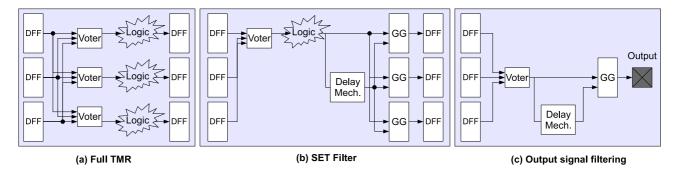

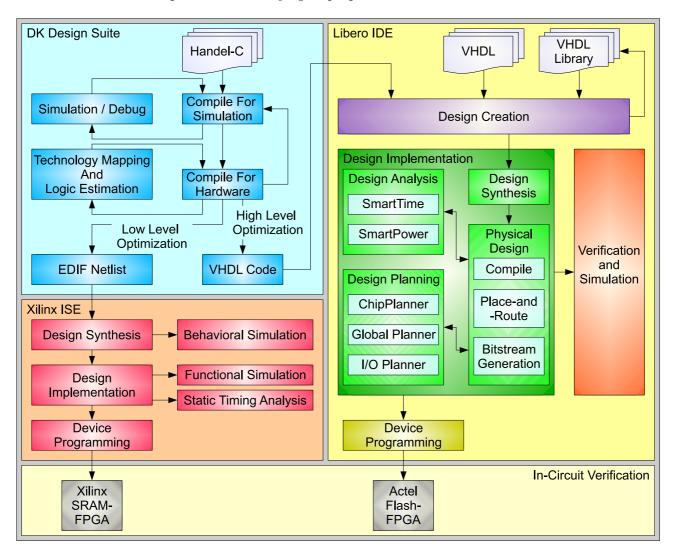

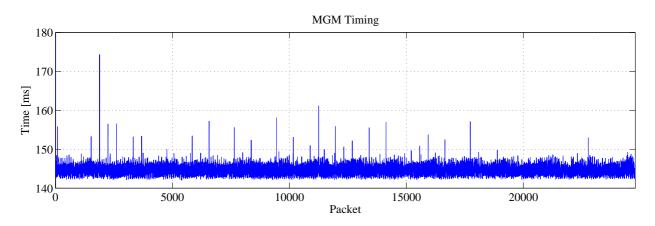

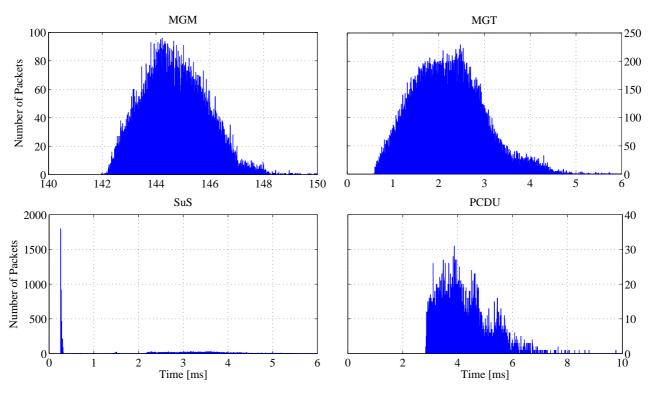

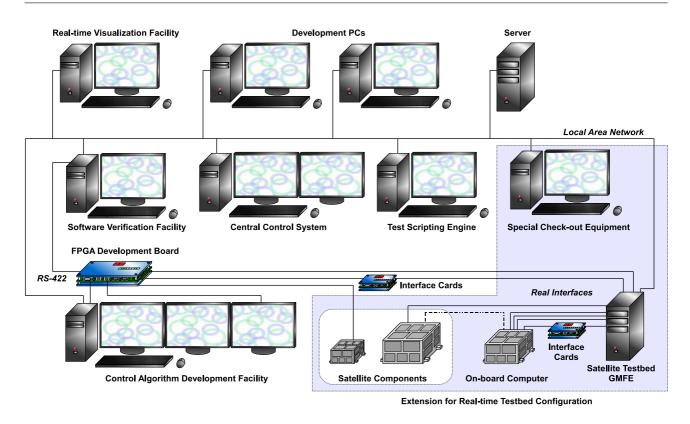

|    |                                                               | 5.5.4. Engineering model of CPN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                                                                                        |                   |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                  |